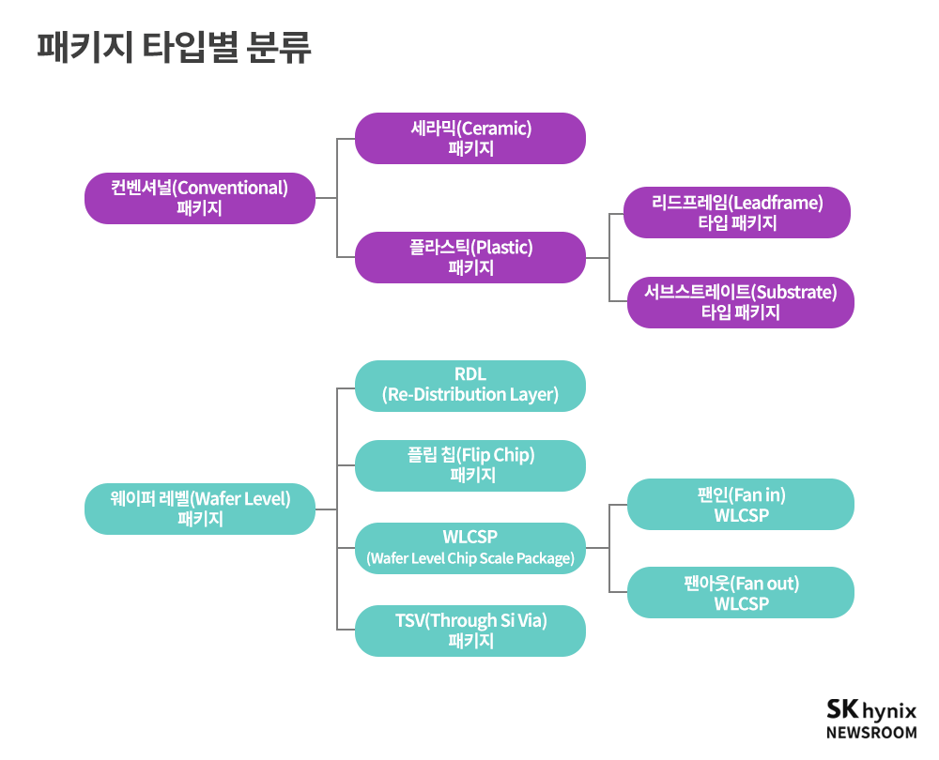

반도체 후공정(6)컨벤셔널 패키지 공정- SK하이닉스 뉴스룸은 컨벤셔널(Conventional) 패키지* 중 플라스틱(Plastic) 패키지 공정의 순서를 나타낸 것이다.리드프레임 타입 패키지와 서브스트레이트 타입의 공정 전반부는 비슷하다.하지만 후반부 연결 핀 구현 방법의 차이 때문에 공정도에 차이가 생긴다. * 컨벤셔널 패키지 : 웨이퍼를 칩 단위로 먼저 잘라서 진행하는 패키지 공정. 참고로 웨이퍼 레벨 패키지는 웨이퍼 상태에서 먼저 패키지 공정을 일부 진행 후 자르는 공정을 의미. (자세한 내용은 3편 참조)▲ 그림 1 : 컨벤셔널 패키지 공정 순서(ⓒ한올출판사) 테스트 완료된 웨이퍼가 패키지 라인에 도착하면 먼저 백 그라인딩으로 원하는 두께가 될 때까지 갈아낸다(Back Grinding).그리고,..