8대 공정으로 MOSFET 형성 체험

(3) 모래로 웨이퍼 만들기

학습목표

웨이퍼 제작 공정에 대해 설명, 세정 방법과 산화막 형성 공정에 대해 설명

학습목차

1. 웨이퍼

2. 세정

3. 산화막 형성

1. 웨이퍼

웨이퍼의 크기가 클수록 생산되는 칩의 수 증가

-> 80년대 4인치 -> 2010~ 12인치

칩 크기 변화시 공정 전체 변화가 수반됨.

웨이퍼의 특성

Si 의 결정구조: FCC (Face Centered Cubic)

단위면적 당 원자수가 많아지면 산화속도는 증가하지만 식각 속도는 감소함

단위면적 당 원자수가 적어지면 문턱전압에 영향을 주는 고정 전하가 줄어들기 때문에

MOSFET의 기판으로는 100을 사용

8인치 이상은 스크라이브 라인을 잘 쓰지 않는다.

다만 플랫존간의 각도에 차이를 둬 표시할 수 있음

칩의 크기는 수율에 영향을 준다. 즉 작을 수록 좋다.

웨이퍼 제작공정 (모래를 잉곳으로 만들기)

2. 세정

단계에 따라 다름

FEOL : Front End of Line (금속 연결 이전 단계)

- 고온 공정 진행 가능

- RCA cleaning 적용, acid, oxidant, plasma 이용

BEOL : Back End of Line (금속 연결 이후 단계)

- post metal cleaning 적용, plasm 이용

RCA: 표준 세정 방식 (습식세정방식) -> 현재는 폐수 감소를 위해 dry 방식 이용

piranha Etch

황산:과산화수소 = 1:1

Oxide strip

산화막 제거에는 불산이 이용됨

HF : 물 = 1:10

SC1

수산화암모늄과 섞어 진행

SC2

염산과 섞어서 진행

Marangoni Drying : IPA 증기와 질소 가스를 이용해 drying mask를 방지하기 위한 건조 방식

Rotagoni Drying : 스핀하며 Marangoni Drying을 적용한 방식

3. 산화막 형성

열산화막 산화 공정

게이트 아래에 산화막 형성

800도씨 이상의 고온에서 진행하는 산화 공정으로 산화막 성장

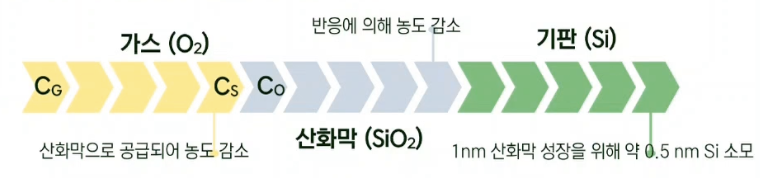

Deal Grove model

- 가스 공급부부터 산화막까지 산화막의 농도는 감소 기판 표면까지도 계속해서 감소

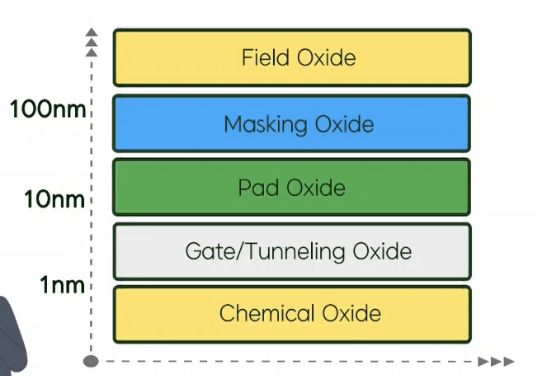

열산화막의 이용

- 두꺼운 산화막 형성(300nm~) -> Mask로 이용

- 얇은 산화막 형성(~30nm) -> 게이트 산화막, 희생 산화막으로 이용

열산화막 형성 이후에는 이온 주입 공정 진행을 위해 Si3N4를 CVD 방식으로 증착함

산화막 형성의 속도 형성 인자

확산과 화학반응 모두 온도의 함수이므로,

온도 증가에 따라 성장 속도 또한 증가함

산화 방식에 따라 성장 속도가 변화하는데

SiO2내 용해도는 수증기(H2)> 산소(O2) 이므로

습식 산화 속도가 건식 산화보다 큼

두께별 용도

산화막 형성 공정의 경우 여전히 개발중에 있음

누설전류

트랜지스터의 소형화 -> 채널 길이 감소 -> 게이트 산화막 두께 감소 -> 산화막에 작용하는 전계 증가

-> 터널링에 의한 누설전류 발생 가능성 증가

=> 고 유전율 게이트 산화막 등장 -> 터널링 방지는 뛰어나지만 지금의 SiO2만큼의 산화막 특성을 따라오긴 어려움 많은 연구 필요

문턱전압

산화에 참여하지 못하고 남은 Si -> 양전하를 띄어 fixed oxide charge로 작용

계면에서 산소와 결합하지 못하고 남은 Danglig bond -> 캐리어를 포획하는 interface trap charge로 작용

=> (100) wafer 사용 및 H2 annealing을 통해 문턱 전압 감소