8대 공정으로 MOSFET 형성 체험

(1) MOSFET이란?

학습목표

MOSFET의 동작 원리 설명, 메모리 산업에서 MOSFET의 중요성 설명

학습목차

1. 접합의 종류 - pn 접합, 금속-반도체 접합

2. MOSFET - 구조, 동작 원리, scaling의 영향

3. 메모리반도체 - 휘발성 메모리, 비휘발성 메모리

1. 접합의 종류

반도체: 도체와 부도체의 중간 영역에 속하는 전기적 성질을 갖는 물질

진성 반도체: 열적 생성된 EHP가 캐리어로 작용

외인성 반도체: 도핑을 통해 캐리어 농도 조절 가능

n type: 15족 원소(P,As)가 Dopant, Donor(전자주개)로 작용

p type: 13족 원소(B)가 Dopant, Acceptor(전자받개)로 작용

외부 전계 인가 여부에 따라 Net Velocity 변화

- 외부 전계가 인가되지 않을 경우

pn 접합 다이오드

다이오드: 전류가 한 쪽으로만 흐를 수 있게 하는 물질

p & n type 반도체 접합 -> 확산(캐리어 이동) -> 공핍영역 생성(dopant이온)

열평형 상태: 균일한 페르미 준위(Ef)

-> banding 정도가 barrier로 작용

순방향 전압(forward bias)인가

-> barrier를 완화해 캐리어 확산이 원활해짐

역방향 전압(reverse bias)인가

-> barrier가 증가해 캐리어 확산이 어려워짐

금속-반도체 접합의 종류

Ohmic contact : 저항 특성, 양방향 흐름

n type : 금속의 일함수 < 반도체 일함수

p type : 금속의 일함수 > 반도체 일함수

Schottky contact : 정류 특성, 단방향 흐름

n type : 금속의 일함수 > 반도체 일함수

p type : 금속의 일함수 < 반도체 일함수

2. MOSFET

기본구조

종류

nMOS = n-channel MOSFET (n channel(전자이동 통로) -> p type 기판, n+ type 소스&드레인)

pMOS = p-channel MOSFET (p channel(전자이동 통로) -> n type 기판, p+ type 소스&드레인

MOS Capacitor: MOSFET의 중앙부를 떼어낸 2단자 소자 형태

nMOS일때, Body는 p type 물질,

Gate에 (+) 전압을 가하면 majority 캐리어인 정공이 밀려남

-> Acceptor 이온이 남아 (-) 형성,

더 큰 (+) 전압을 가하면

정공이 밀려나는 것으로 대응하지 못해 minoirty 캐리어인 전자가 다가옴

-> Inversion layer 형성

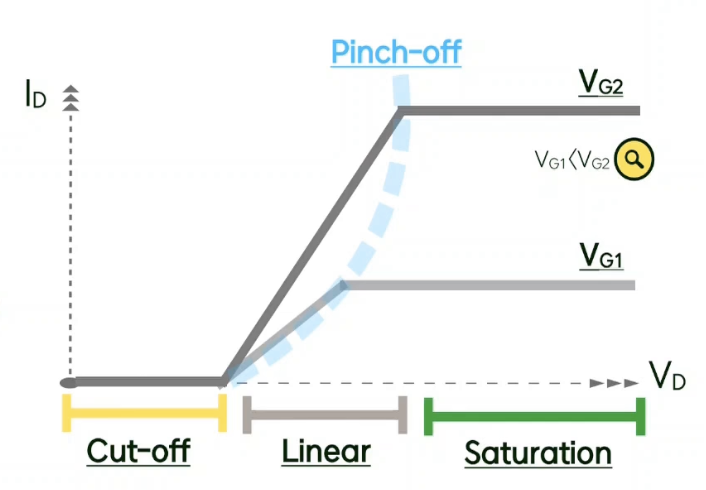

V-I Curve

ID: 드레인 전류

- 채널을 지나가는 캐리어들이 만드는 전류

VD: 드레인 전압

- 채널에 있는 캐리어를 끌어 당기는 역할

VG: 게이트 전압

- 채널의 폭과 두께를 넓여 캐리어 이동을 돕는 역할

Vth: 문턱 전압

- 소스에서 드레인으로 전류가 흐르기 시작할 때,

게이트에 가해진 전압

Cut-off Region(차단 영역): 채널이 형성되지 않아 VD가 가해지더라도 ID는 0인 상태 VG<Vth

Linear Region(선형 영역): channel이 형성되어 VD 증가에 따라 ID가 증가하는 상태 VG> Vth , VD<VG-Vth

Pinch-off: 소스와 드레인의 공핍영역 증가로, 채널이 끊기는 현상

Saturation Region(포화영역): 채널의 단락지점(pinch off)이 드레인에서 멀어져 길이는 짧아지지만, VD의 증가로

가속된 전자가 드레인으로 이동하여 ID가 일정한 값을 갖는 영역

VG> Vth , VD>VG-Vth

[Scailing의 영향]

Moore의 법칙: 반도체 칩의 집적도는 2년마다 2배로 증가

단채널 효과: 게이트 길이 감소에 따라 문턱전압이 감소하는 효과 (SCE, Short channel Effect)

열전자 효과: 채널 길이 감소 - 소스&드레인 사이의 전계 증가 - 기판의 Si격자와 충돌해 이온화 (기판 전류 형성)- oxide 층을 넘어 게이트로 이동 (게이트 전류 형성) - 포획(문턱전압 상승)

Punch-through : 소스&드레인 공핍영역 접합- 게이트 전압으로 제어 불가, 기판의 아래쪽에 캐리어 이동 통로 형성, 의도치 않은 큰 전류 생성

드레인 전압에 의해 확장되는 공핍영역 중, 모서리 부분의 기판 도핑 농도를 증가시켜 확장방지.

3. 메모리 반도체

휘발성메모리

SRAM = refresh가 필요 없고(Static) 임의의 메모리 주소에 접근(Random Access Memory)

6개의 트랜지스터를 사용 (CMOS 2, nMOS2)

CMOS(nMOS, pMOS로 구성) -> 1개당 2개의 Tr

전원이 공급되면 값을 유지하고 꺼지면 유지가 불가한 휘발성 메모리

DRAM = refresh가 필요하고(Dynamic) 임의의 메모리 주소에 접근(Random Access Memory)

1개의 트랜지스터와 1개의 캐패시터 사용

nMOS: 스위칭 소자

캐패시터: 데이터 저장장치

마찬가지로 휘발성 메모리

*refresh란 누설 전류로 인해 캐패시터에 저장된 전하가 감소하므로, 일정 주기로 전하를 올려주어 저장된 값을 유지하는것

비휘발성 메모리

NAND flash

flash 메모리: 메모리 셀을 한 번의 동작만으로 Program/ Erase 가능한 소자

셀 연결 방법에 따라 2가지로 구분 가능 -NOR: 병렬, 빠른 처리속도 / -NAND: 직렬, 큰 저장용량

*Program: 기판에서 FG(Floating Data)로 FN 터널링 방식으로 전자 이동

Erase: FG내 모든 전자를 꺼내는 과정

FG 내의 전자 개수별 문턱 전압의 분포를 사용해 여러 데이터를 저장, 전원이 꺼져도 전하는 그대로 존재