8대 공정으로 MOSFET 형성 체험

(2) Fab에 입장하다

학습목표

반도체 8대 공정에 대해 설명할 수 있다, FAB의 구조에 대해 설명할 수 있다.

학습목차

1. 8대 공정

2. Fab

1. 8대 공정

1. 웨이퍼 제조 공정

웨이퍼의 재료는 주로 실리콘

- 지구상에 양이 풍부함

- 밴드갭이 크고 열적 안정성이 높음

- 도핑에 유리함

- 무독성

- 산화막 특성이 우수

웨이퍼 제조 방법

- 웨이퍼란?

반도체를 성장시켜 만든 단결정 기둥을 얇게 썰어낸 원판

*단결정 기둥(잉곳):

Czochralski Method(초크랄스키 기법)(CZ) -> 도가니를 사용한 방식 / 대부분 기업이 사용하는 방식

Flat zone Growth(플랫존성장)-> RF코일을 이용, 도가니를 사용하지 않아 순도가 더 높음 / 다만 생산성이 떨어져

기업보다는 연구실에서 사용

*기둥 가공

Slicing - Lapping - Etch - Polishing(+Edge grinding) - Inspection -> Bare Wafer (아무런 작업도 하지 않은 웨이퍼)

2. 산화막 형성 공정

산화막의 기능

- 절연막: 회로 사이의 누설 전류 차단

- 보호막: 확산 방지막 -> 이온 주입 공정 진행시, mask로 사용

식각 방지막 -> 식각 공정에서 남기고 싶은 곳의 mask로 사용

자연 산화막

실리콘은 산소와 쉽게 반응하므로 공기 중에 노출되는 Si 표면에는 SiO2가 생성되고 cleaning 과정에서 제거가 필요함

형성 방법

- CVD (모든 기판에서 사용 가능)

SiH4+O2 -> SiO2 + H2

SiH4+2NO2 -> SiO2 + 2N2

- 열산화 (막질이 우수, 대부분 기업에서 이용)

Si + O2 -> SiO2 건식 산화

Si + 2H2O -> SiO2 + 2H2 습식 산화

3. 포토 공정

포토 공정의 단계

cleaning -> HMDS 도포 -> PR 도포 -> soft bake -> Align(정렬) + Exposure(노광) -> PEB(노광 후 열처리)

-> Develop(현상) -> Hard Bake

포토레지스트

- positive PR : 노광된 부위가 현상시 제거되는 PR

- negative PR : 노광된 부위가 현상시 잔류하는 PR

-> 파장이 짧은 UV를 사용하므로 내부는 파장이 긴 노란색 조명을 사용함(Yellow Room)

노광 방식

- 접촉 노광법 : 웨이퍼와 마스크를 접촉하여 정렬하는 방법 -> 이물질이 많고 마스크가 손상될 수 있다.

- 근접 노광법 : 웨이퍼와 마스크 간 gap을 형성해 정렬하는 방법 -> 해상도가 떨어지고 회절이 높다.

=> 투사 노광법 : 반사와 굴절을 이용해 문제점을 개선한 방법

4. 식각 공정

건식 식각 (dry etch)

(주로 플라즈마 이용)

반응성 기체, 이온을 이용해 특정 부위를 제거

이방성 특징을 가져 미세회로 형성에 유리

습식 식각 (wet etch)

용액을 사용해 화학 반응을 통해 물질을 제거

선택비가 높지만 등방성 특징을 가짐

플라즈마

고체, 액체, 기체를 넘어선 제4의 상태

자유전자, 이온, 라디칼로 구성

상압에서는 강한 에너지가 요구되지만

저압 상태에서는 비교적 적은 전계만으로도

열전달을 형성해 플라즈마를 얻을 수 있음

플라즈마 속 라디칼이 웨이퍼 위의 원자(박막)과 만나

강한 휘발성을 띄는 물질을 생산해 제거하는 방식

5. 이온 주입 공정

도핑에는 확산과 이온주입의 방식이 있음

확산

- 농도 차이에 의해 평행 상태에 도달할 때 까지 입자들이 이동

-> 등방성 이동으로 채널 길이가 짧아짐

(1) Pre-deposition: oxide를 마스크로 사용해 원하는 부분만을 도핑

(2) Drive-in: 온도를 증가시켜 원하는 깊이만큼 dopant 확산 (예시 Si기판에 B확산)

Pre-deposition: B2H6 + 2O2 -> B2O3 + 3H2O

B 확산: 2B2O3 + 3Si -> 3SiO2 + 4B

Cap-oxidation: 2H2O + Si -> SiO2 + 2H2

이온 주입

- 이온 빔을 사용해 특정 위치에 집중적으로 도핑하는 방식

-> 이방성 이동으로 정확한 위치선정 가능

(1) 양이온 생성: 열전자 방출을 통해 가스로부터 양이온 생성

(2) 양이온 분류: 자기장을 가해 질량에 따른 경로차이로 이온빔에 사용할 원하는 이온만을 분류

(3) 이온빔 주입: 빔 전류를 측정해 dopant의 양 조절

6. 박막 형성 공정

PVD

- 물리적으로 흡착되는 방식, step coverage가 낮아 주로 금속에서 사용

sputtering: 플라즈마를 사용해 타겟 물질을 떼어내 기판에 흡착시켜 박막을 형성하는 방식

Evaporation: 가열(저항열, 전자빔)을 통해 물질을 기화시키고 기판 도달 시 응축을 통해 박막을 형성하는 방식

CVD

- 박막전구체를 수증기 형태로 공급해 증착하는 방식 -> 공정 조건에 따라 여러 방식 존재

APCVD: 대기압, 400~500도씨

LPCVD: 0.1~10Torr, 300~800도씨

PECVD: 라디칼을 사용해 반응에 필요한 에너지 감소

열CVD: 저항, 유도 가열 방식으로 반응물 생성

ALD: 원자층 증착법 - CVD 방식과는 차이가 있지만 화학반응을 이용한다는 부분에서 유사한 방식

-> 최근 기업에서 많이 이용

-> 한 과정에 원자층 한 층의 증착층이 생김

7. 금속 배선 공정

재료 선택

- 낮은 비저항 (Ag<Cu<Au<Al)

- 쉬운 제작 공정 및 높은 부착력으로 형성에 유리해야함

- 식각이 용이해야함 (식각시 휘발성 부산물 생성 필요)

- 높은 열적, 화학적 안정성과 미세화 가능성으로 신뢰도가 있어야함

Al 배선

- 증착과 식각에 유리함 / electromigration 과 junction spiking 문제 발생

*electromigration: 얇은 박막이나 (thin film) wire 형태의 전도체에 높은 전류밀도가 가해질때

Mass transport가 일어나는 현상. hillock, bridge, void같은 defect가 생겨 device 성능 저하를 초래

*junction spiking: 높은 온도의 반도체 공정에서 Al과 Si가 activity difference에 의해 interdiffuse(상호확산)

되면서 발생하는 현상. device에 short를 일으켜 오작동 하게 만들 수 있음 -> Al내에 1%의 Si를 첨가한 합금(alloy)를

사용하면 됨.

Cu 배선

- 비저항이 매우 낮은 공정으로 electromigration이 적어 미세화에 유리함

- 건식 식각은 어려움

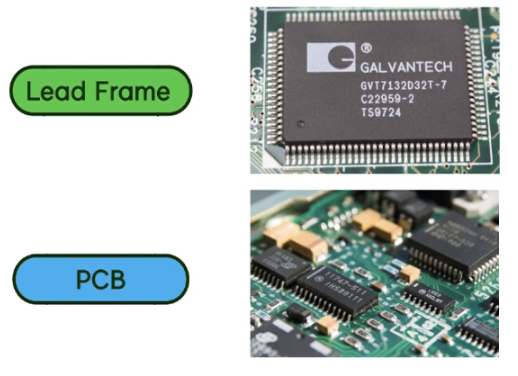

8. 테스트 및 패키징 공정

테스트진행

EDS: 웨이퍼 완성 단계에서 진행하는 검사

Packaging: 조립 공정 이후 검사 진행

품질 테스트: 출하 전 단계에서 진행하는 검사

패키징: 외부로부터 보호하며 전기적으로도 보호하는 과정

2. Fab

1. 장비사를 제외하고 나면 반도체 기업은 세 가지로 나눌 수 있다.

IDM : Intergrate Device Manufacturer

- 설계와 생산을 모두 담당하는 기업

ex) 삼성전자, SK하이닉스, 인텔

Fabless : Fabrication + less

- 생산은 하지 않고 설계만 담당하는 기업

ex) 애플, 퀄컴

Foundry : 위탁 생산 전문업체

- 고객사의 요청에 따라 공정을 진행해 완성된 웨이퍼를 납품

- 주로 완성된 제품(패키징 완료)이 아닌 웨이퍼 상태로 납품하여 다른 업체에서 패키징을 진행

ex) TSMC, 삼성전자, UMC

2. Fab의 구조

청정 시스템 : 이물질을 제거하며 적절한 온습도, 압력을 유지하기 위한 시스템

- 풍도: 하강기류를 만들어 먼지를 내보내고 난류 방지

- 클린룸: 난류가 생기지 않는 양압 분위기의 오염 제어 구역

- 서브 팹: 부대 설비가 위치하는 공간

-> 나노 단위의 미세 회로를 다루기 때문에 오염물은 반도체 품질에 치명적이다.

물류 자동화 시스템

- OHT: Overhead Holst Transport

자율주행을 통해 FOUP을 이송

클린룸 천장의 레일을 따라 이동

다양한 센서 탑재, 중앙 컨트롤러와의 정보 전달을 이용해 문제 발생 시 경로 변경 및 속도 조절

- FOUP: Front Opening Unival Pod

불순물로부터 보호

적재, 이송에 용이

공정 장비에 들어가 공정을 진행한 뒤 다시 보관

맵핑을 통해 개수 확인 및 정렬