(2) 반도체 공정과 산화 : SK하이닉스 뉴스룸

반도체 공정 둘러보기

우리는 지난 콘텐츠 마지막 부분에서 모스펫(MOSFET)은 마치 붕어빵 찍어내듯 만들 수 있다는 것과

BJT¹등과는 달리 납땜 등의 과정이 필요 없다는 것을 확인했다.

당장 주변의 전자기기를 하나 분해해 보면 기판 위에 트랜지스터, 건전지, 축전지, 코일 등 다양한 단위 소자가

PCB²기판 위에 납땜돼 올라가 있음을 알 수 있다. 쉽게 말하면 ‘소자 제조 → 소자 연결’ 의 순서로 만들어진다.

¹BJT(Bipolar Junction Transistorz) : 양극성 집합 트랜지스터, 반도체 내부에서 P형 반도체와 N형 반도체의

두 영역 사이의 경계부분을 일컫는 PN 접합을 이용해 만든 트랜지스터를 의미한다.

²PCB(Printed Circuit Board) : 인쇄회로기판, 전자 회로를 하나의 판에 넣고 표면에 부품들을 납땜하는 것으로

대부분의 전자기기에 들어간 반도체 기판이다.

웨이퍼 가공 첫 단계에 해야 할 일은 다양한 형태의 단위 소자를 만드는 것이다.

실제로는 실리콘 웨이퍼 위에 각종 처리를 해서 필요한 개수의 소자를 새기는 것에 가깝다.

이 과정을 FEOL(Front End Of the Line: 공장 내에서 하는 앞단계)이라 부른다.

그 이후에는 납땜에 해당하는 일을 해야 한다. 하지만 이렇게 작은 소자들을 직접 납땜할 수는 없다.

대신 FEOL에서 사용한 것과 비슷한 기술들을 이용해

매우 미세한 배선을 만들어 수십억 개의 단위 소자들을 서로 연결한다.

이 과정을 BEOL(Back End Of the Line)이라 부른다.

그리고 이 두 과정을 합쳐 웨이퍼 가공 과정인 ‘전공정’이라 부른다.

앞으로 배울 산화, 포토, 식각 등 다양한 공정들은 전부 FEOL과 BEOL 과정에서 사용되는 수단일 뿐이다.

각 단계의 목적에 따라서 특정 장비를 사용하는 빈도와 횟수가 달라질 뿐이며, 기본 목적은 똑같다.

미세한 패턴을 아주 많이 만들어내는 것이다.

일반적으로 알려져 있는 반도체 8대 공정은 웨이퍼 제조, 산화, 포토, 식각, 증착, 금속 배선, 테스트, 패키징이다.

하지만 위와 같은 분류는 주의해 받아들여야 한다.

위 그림을 보면 알 수 있겠지만, 웨이퍼 제조는 엄밀하게 반도체 공장 내에서 일어나는 일이 아니다.

또한 금속 배선, 패키징, 테스트의 경우 포토, 식각, 증착 등과 같은 단일 공정이 아닌

목적을 가진 특정 작업 전체를 아우르는 범주임을 알 수 있다.

유리 씌우기 : 산화

그림 2에 따르면, 반도체 제조 공정은 맨 아래에서 시작해 위를 향해 쌓아 올리는 방식으로 진행됨을 알 수 있다.

이 과정은 단순히 균일한 물건을 시루떡처럼 쌓아 올리기만 하는 과정은 아니다.

다양한 모양들을 반도체 내부에 균일하게 만들어 내기 위해서는 필요 없는 부분을 깎고,

필요한 부분은 물질을 씌우는 등의 다양한 작업을 해야 한다.

이러한 작업에는 반응성이 높은 다양한 화학 물질이 사용되기 때문에,

화학 물질이 원치 않는 곳에 도달할 경우 반도체 제조가 제대로 되지 않을 수 있다.

그뿐만 아니라, 반도체 내에는 서로 직접 맞닿아 합선돼서는 안 되는 부분들도 존재한다.

따라서 일종의 차단막을 만드는 방법이 있어야만 한다. 여기 사용하는 공정이 산화 공정이다.

산화 공정은 실리콘 웨이퍼 위에 보호막을 씌우는 과정이다.

실리콘(Si)은 산소와 반응하면 유리(SiO₂)가 된다.

우리가 일상생활에서도 알 수 있듯, 유리는 튼튼할 뿐만 아니라 반응성이 적어

각종 음료수는 물론 염산이나 황산 등의 화학 약품을 저장하는 경우에도 사용된다.

이는 반도체에서도 마찬가지다. 산화 공정을 통해 생성된 산화막은 튼튼할 뿐만 아니라 매우 안정적이다.

산화막은 다른 물질의 진입을 차단하므로 이온 주입 공정¹ 등에서 요긴하게 사용된다.

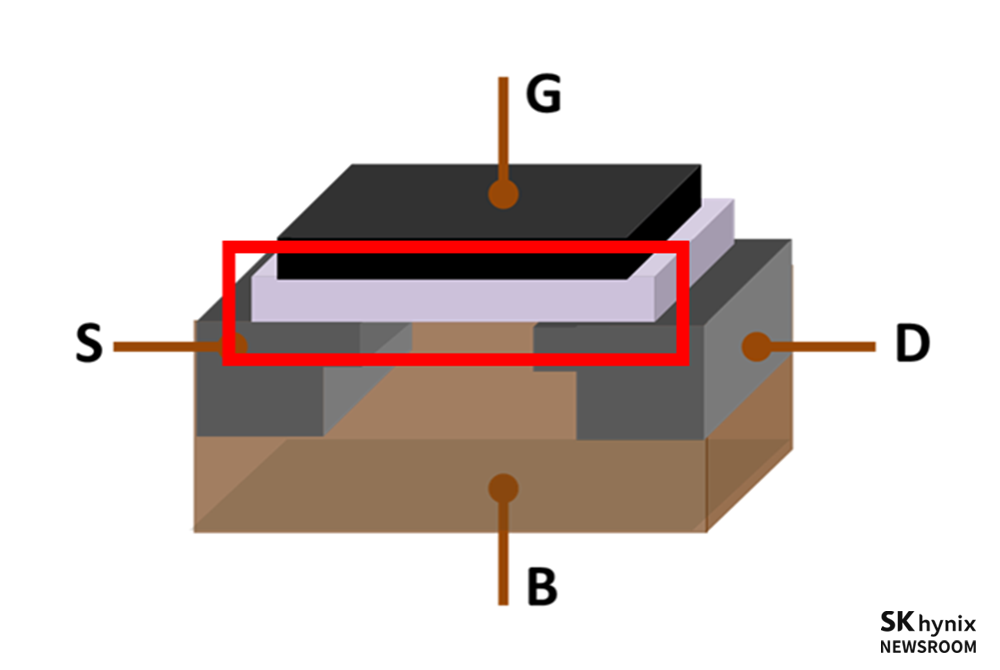

산화막은 의도적으로 전류 흐름을 막기 위해서도 사용된다. 모스펫 구조의 핵심은 게이트이다.

과거의 BJT와 같은 트랜지스터와는 달리,

모스펫은 게이트가 전류 통로(S-D사이 영역)에 직접 맞닿지 않고‘간접적’으로 영향력만을 행사한다.

모스펫이 가동 중이 아닐 때는 전력 소모가 적은 이유이다.

여기서 게이트와 전류 통로를 막는 물질도 산화막이 사용되곤 한다.

이를 특별히 게이트 옥사이드(Gate Oxide)라고 부른다.

물론 최근 생산되는 첨단 반도체들의 경우, 반도체 크기가 작아짐으로 인해

게이트 절연막으로 HKMG² 등 다양한 대체 물질이 사용되고 있다.

¹이온 주입 공정(Ion Implant) : 반도체 제조 과정에서 순수한 실리콘 웨이퍼를 반도체로 바꾸기 위해 3족이나 5족 이온을 주입하는 과정.

²HKMG(High-K Metal Gate) : 누설전류를 효과적으로 줄일 수 있도록 개발된 새로운 모스펫 게이트.

기존에 다결정 실리콘(Polysilicon)이던 게이트는 금속으로 대체하고, 산화규소였던 절연막은 고유전체(High-K)로 대체한 트랜지스터.

참고로, 반도체 회사가 보호막으로 사용하는 물질은 이산화규소(SiO₂)만 있는 것은 아니다.

필요한 경우 증착의 형태로도 보호막을 씌우거나, 이미 형성된 회로 일부분을 제조 과정에서 활용하기도 한다.

당연하지만 산화는 웨이퍼 물질의 일부를 사용하는 과정이다.

산화 공정 과정에서 웨이퍼를 이루는 실리콘 원자가 상당량 소모된다.

이는 이후에 읽어보게 될 ‘증착’ 과정과 큰 차이점이므로 미리 기억해 두는 것이 좋다.

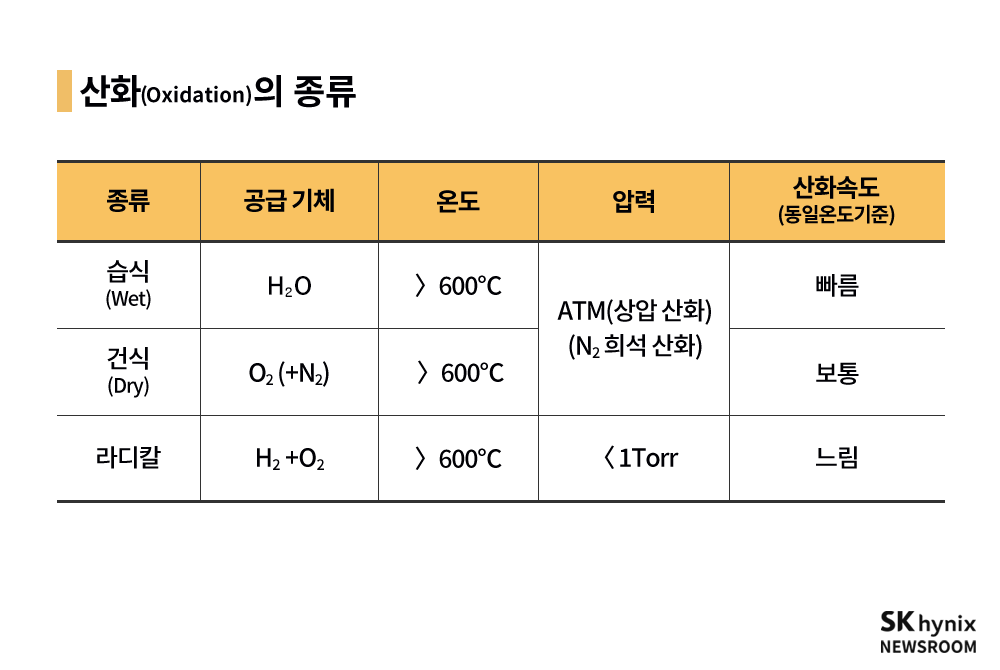

산화 공정의 종류

산화 공정은 습식(Wet), 건식(Dry), 라디칼(Radical) 크게 3종류로 나눌 수 있다.

습식, 건식이라는 단어는 이후에도 자주 보게 될 것이니 미리 익혀두면 도움이 될 것이다.

습식 산화는 실리콘 웨이퍼를 고온의 수증기(물)와 반응시키는 방식이다.

아래의 화학 반응을 통해 실리콘 산화막을 생성하는 것이다.

Si (고체) + 2H₂O (기체) → SiO₂ (고체) + 2H₂ (기체)

공식을 쓰긴 했지만, 쉽게 말하면 고온의 물을 통해 실리콘 표면을 녹슬게 하는 것과 비슷하다고 생각하면 된다.

습식 공정의 경우 매우 빠른 속도로 실리콘 산화막을 성장시킬 수 있는 반면

산화막의 전체적 균일성, 밀도 등의 특성이 떨어진다.

또한 이 과정에서 부산물인 수소가 생성된다.

특성의 조절이 쉽지 않기 때문에, 성능에 큰 영향을 끼치는 핵심 영역에서 사용하기는 힘들다.

건식 산화의 경우 고온의 산소 기체를 직접 실리콘 웨이퍼에 보내주는 방식이다.

산소 분자는 물 분자보다 무겁기 때문(32 vs 18)*에 실리콘 웨이퍼 내부로 침투하는 속도가 상대적으로 좀 더 느리다.

따라서 이 방식은 생성 속도가 습식 산화에 비해 느리다.

대신 습식 산화와는 달리 부산물 기체(H₂)가 생기지 않을 뿐만 아니라,

밀도가 높고 균일한 산화막을 생성시킨다.

이러한 특성으로 인해 최종 제품의 성능에 중요한 영향을 미치는

반도체 게이트 부분의 산화막은 건식 산화로 만들어지게 된다.

라디칼 산화는 위에서 살펴본 두 산화와는 다소 다른 과정으로 진행된다.

위의 두 산화 과정은 자연 기체들을 고온으로 올려 에너지를 줌으로써 웨이퍼 표면과 반응시키는 방식이었다.

라디칼 산화는 한 단계를 더 거치는 방식이다.

산소 원자를 고온에서 수소 분자와 섞어주면 라디칼이라는 반응성이 높은 기체로 바뀌는데,

이들을 실리콘 웨이퍼와 반응시키는 방식으로 이뤄진다.

라디칼은 반응성이 높아 건식 산화보다도 훨씬 높은 품질의 산화막을 형성할 수 있다.

불완전하게 반응하는 경우가 적기 때문이다.

*수소(H)의 원자 무게를 1이라고 했을 때 산소(O)의 원자 무게는 16.

산소(O2)의 분자 무게는 32, 물(H2O)의 분자 무게는 16이므로 산소의 분자가 더 무겁다.

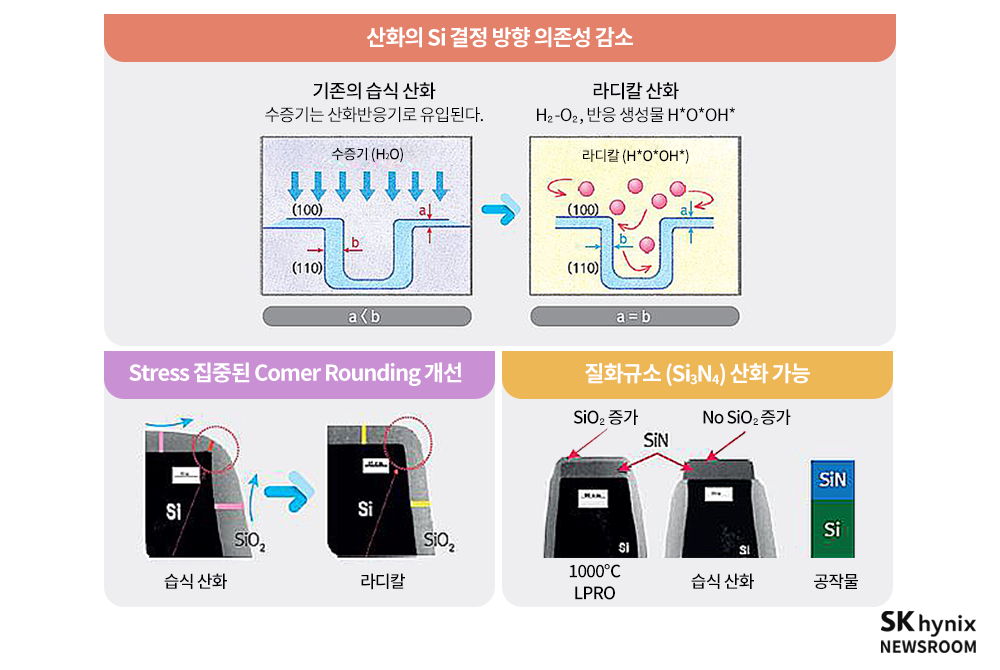

또한, 라디칼 산화를 이용하면 입체적 구조에서도 산화막의 두께를 균일하게 가져갈 수 있다.

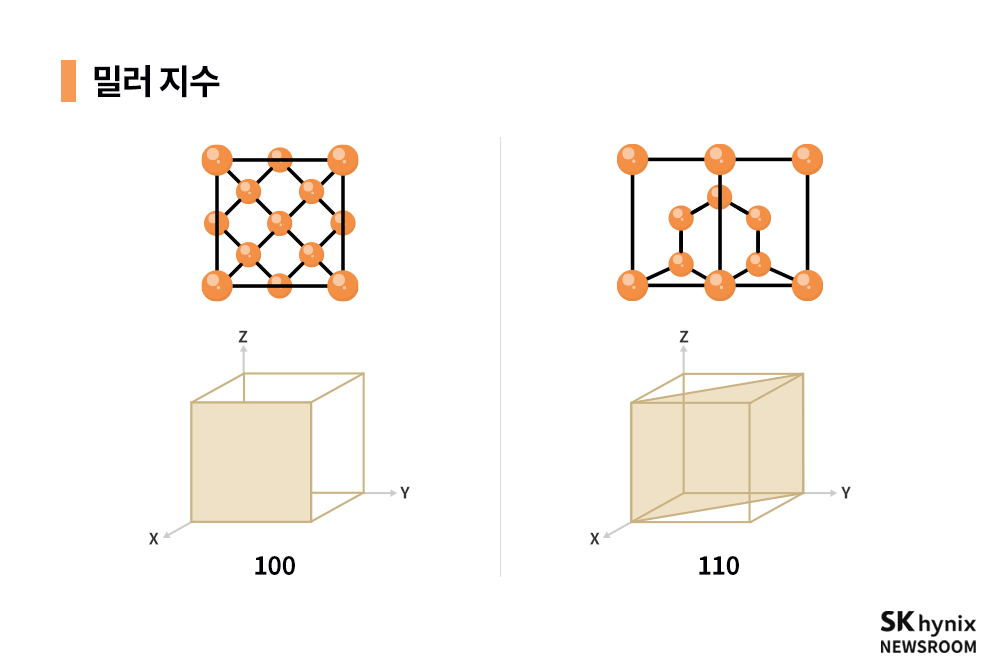

반도체 회사가 사용하는 실리콘 웨이퍼는 단결정으로, 웨이퍼 표면 전체의 실리콘 원자들이 전부 같은 방향의 결정을 가지고 있다.

위 그림에 나오는 100, 110과 같은 숫자가 실리콘 결정의 방향이며, 아래 그림은 실리콘 원자들을 바라본 그림이다.

두 그림을 보면 알 수 있지만, 습식과 건식 산화의 경우 웨이퍼 위 방향(100)의 산화막 형성 속도는 느리고,

옆(110) 방향의 산화 속도는 빠르다. 그 이유는 100방향에 배치된 규소 원자가 더 촘촘하기 때문이다.

원자가 촘촘하게 배치돼 있으면 건식이나 습식 산화 기체가 결정을 뚫고 들어가 반응하기 힘들다.

라디칼 산화의 경우 이런 문제에서 좀 더 자유롭다.

그뿐만 아니라 라디칼 산화는 기존에는 산화막을 만들기 힘들었던 모서리 부분에도 균일한 산화막을 생성시키며,

심지어는 반응성이 낮은 편에 속하는 질화규소(Si₃N₄)*에서도 실리콘 원자를 훔쳐(!) 산화 반응을 일으키기까지 한다.

반도체의 미세화가 어려워짐에 따라서, 반도체 회사들이 반도체에 3차원 구조를 도입하는 일이 많아지고 있다.

이로 인해 균일한 고품질의 막을 만드는 기술은 점점 더 반도체에서 중요해지고 있다.

이는 산화 공정에서도 마찬가지다.

*질화규소(Si₃N₄) : 질화규소는 보호막 역할을 하는 소재 중 하나로 반도체 소자 제조 과정에서 증착 방식으로 씌워진다.

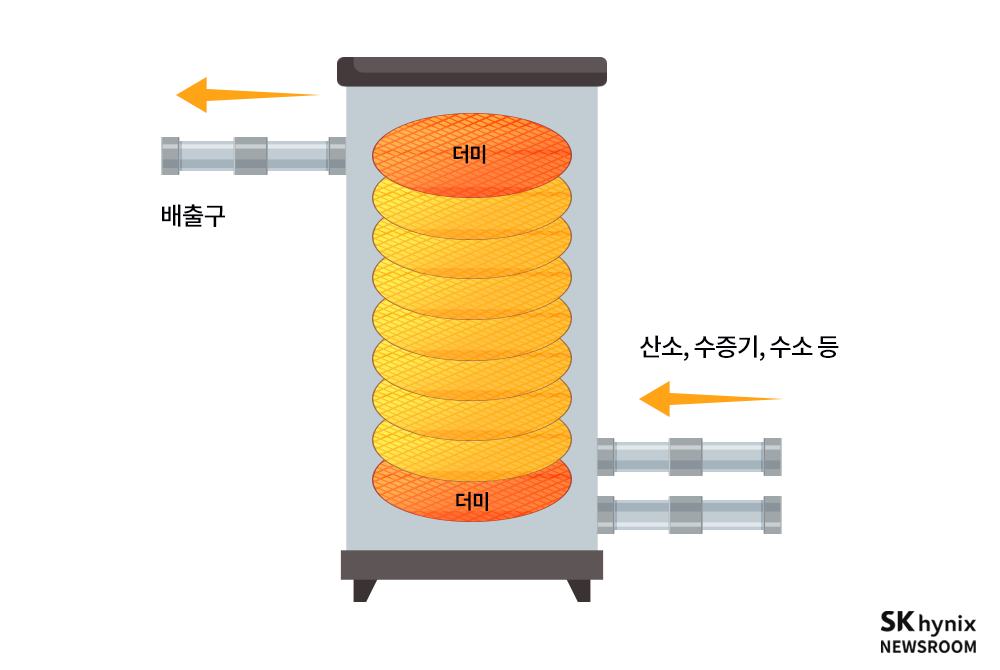

아래의 그림 6은 매우 간단하게 그린 산화 장비의 구조다. 실제로 사용하는 장비들은 훨씬 복잡한 구조임을 기억할 필요가 있다.

장비에는 기체 투입구가 있는데, 해당 주입구에 반응시키고자 하는 기체를 주입해 준다.

주입된 기체는 내부에서 가열되고, 웨이퍼와 만나서 반응하게 된다.

투입된 웨이퍼 안에는 일부 더미 웨이퍼가 끼워져 있다.

더미 웨이퍼는 기기 구조상 발생할 수밖에 없는 기기 양 끝 웨이퍼들의 반응속도 차이를 메워줄 목적으로 투입된다.

또한 그림을 통해 알 수 있겠지만 산화 과정은 처리 속도가 상당히 빠른 축에 속한다.

수십 개의 웨이퍼를 일제히 투입한 뒤 반응시키기 때문이다.

이번 콘텐츠에서는 간단하게 전체 제조 공정 개괄과 산화 공정에 대해서 살펴봤다.

우리는 이해를 돕기 위해 이미 친숙한 단어인 8대 공정이라는 용어를 중심으로 각 공정을 설명하고 있지만,

실제로는 확산(Diffusion) 공정의 한 분야이기도 하며, 온도를 기준으로는 고온 공정으로 분류된다.

다음 편에서는 빛을 이용해 웨이퍼에 전자 회로를 새기는 노광 공정에 대해 알아보고자 한다.

출처:

1. https://news.skhynix.co.kr/post/jeonginseong-column-oxidation

[반도체 전공정 2편] 반도체 공정 개괄과 산화 (2/6)

우리는 지난 콘텐츠 마지막 부분에서 모스펫(MOSFET)은 마치 붕어빵 찍어내듯 만들 수 있다는 것과 BJT등과는 달리 납땜 등의 과정이 필요 없다는 것을 확인했다. 이번 콘텐츠에서는 그 과정들을

news.skhynix.co.kr

'반도체 > 반도체 전공정' 카테고리의 다른 글

| [반도체 전공정] (6) 금속배선 공정 / 배리어 메탈 / Damascene (0) | 2024.06.18 |

|---|---|

| [반도체 전공정] (5) 증착 공정 / STI / IMD / 균일도 / 스텝커버리지 / 갭필 / ALD / 일렉트로마이그레이션 (0) | 2024.06.17 |

| [반도체 전공정] (4) 식각 공정 / RIE(Reactive Ion Etching : 반응성이온식각) / (0) | 2024.06.16 |

| [반도체 전공정] (3) 포토 공정 / 포토레지스트 / 포토마스크 / 현상 / BARC / 오버레이 / PEB (1) | 2024.06.12 |

| [반도체 전공정] (1) 컴퓨터, 트랜지스터의 탄생과 반도체 (1) | 2024.06.11 |