무어의 법칙, 트랜지스터

무어의 법칙

: 1964년 인텔 공동창립자인 고든 무어가 동일 면적 내 집적되는 소자 개수가 1년마다 2배가 될 것이라고 예측

(이후 18개월 마다로 수정함)

지난 40여년간 무어의 법칙이 지켜졌지만, 현재 물리적 한계에 직면해 무어의 법칙이 완벽히 들어맞지는 않음

반도체의 집적도가 올라가거나 IC chip크기가 작아지도록 노력하는 중

(동일한 면적에 트랜지스터 개수 증가, = 트랜지스터 소자 스케일링)

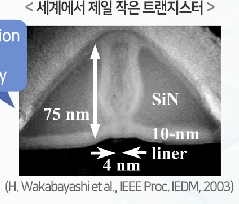

10나노, 8나노 공정 등~ → 트랜지스터의 게이트 길이를 의미함

chip사이즈를 줄이는 공정. ⇒ 다양한 회로를 추가할 수 있음

게이트 길이를 절반 줄일경우 chip면적은 네배를 줄일 수 있음

트랜지스터(Transistors)

: 반도체를 이용하여 전자신호 및 전력을 증폭하거나 스위칭 하는 데 사용되는 반도체 소자

일반적인 저항은 V=IR 로 직선이지만,

트랜지스터의 경우 비선형 구간이 존재해 전압을 변화시켜도 전류가 변화하지 않는 포화영역이 존재함

(스위칭특성,증폭기역할)

양극성 접합 트랜지스터(Bipolar Juction TR, BJT)

- 두 개의 PN 접합이 등을 맞대고 합쳐진 형태 (npn형, pnp형)

- 3개의 단자 (베이스(Base), 컬렉터(Collector),에미터(Emitter)의 3단자로 구성)

- 베이스 전류의 작은 변화는 컬렉터 전류의 매우 큰 변화로 나타남

에미터와 컬렉터 사이에 npn접합이 존재하고, 베이스는 P형 반도체와 접해있음

- 베이스 단자의 전압을 변화시킴으로써 P형 반도체의 전기전도도를 변화시켜 에미터와 컬렉터 사이의 전류변화를 유도 → 트랜지스터가 동작하는 원리

작은 베이스 전류를 조절하여 컬렉터와 에미터 사이의 큰 전류를 조절할 수 있음

MOSFET 트랜지스터(MOS Field Effect TR)

- 드레인(Drain), 소스(Source), 게이트(Gate) 3단자로 구성

- 몸체(Body)전극을 추가하여 4단자로 표현되기도 하나, 보통 소스와 몸체를 단락시켜 활용함

- 금속-절연층 반도체 구조에 전기장을 인가하여 반도체 표면에 전기적 채널을 생성하거나 없앰 → 전기전도도 조절

- BJT에 비해 동일한 성능이지만 더 작은 구조로 제작 가능함

- 게이트 단자에서 소모되는 누설적류가 작고, 전력소모가 작음. 디지털 및 아날로그 IC에 폭넓게 사용됨

게이트 전극 금속(Metal) 아래에 산화막(Oxide), 그 아래 실리콘 반도체 (Semiconductor(P형실리콘)) → MOS

양의 전류 흘릴 경우 P형 실리콘의 국소적인 면적이 N형 실리콘으로 변화 → 전기전도도가 상승하여 전류가 흐를 수 있음

이 경우 소스와 드레인 영역이 N형 반도체, 그 사이도 N형 반도체 -> 전기전도도 상승, 전류가 흐를 수 있는 상황

음의 전류가 게이트에 흐를경우 P형 실리콘에는 정공이 유도, 소스,드레인은 N형이므로 정공이 그 사이를 통과X

→ 소스/드레인 사이에 전압을 인가해도 전류가 흐르지 않음.

즉. P형 MOSFET(전자가 흐르는 개념)과 N형 MOSFET(정공이 흐르는 개념 )은 반대임

결론: 게이트 전압을 조절하여 소스/드레인 사이의 전류 흐름을 임의대로 조절할 수 있음

'반도체 > 기타 반도체 관련 지식' 카테고리의 다른 글

| [반도체 기초] 개념과 재료특성 (1) | 2024.01.08 |

|---|